| Мова : |

|

| Енциклопедія співтовариство |Енциклопедія відповіді |Відправити запитання |Словник знань |Завантажити знання |

Binary Counter |

|

|

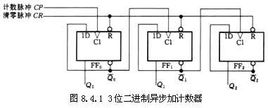

Лічильник занадто великі цифрові системи, що використовують основні логічні пристрої. Воно не тільки може записати кількість імпульсів вхідних тактових, також може досягти частоти, часу і послідовності імпульсів генерації такої биття пульсу. Наприклад, комп'ютер Тактовий генератор, роздільники, лічильник команд, і т.д. повинні використовувати лічильник. Багато різних типів лічильників. Різні режимі імпульсний вхід годинник можна розділити на синхронної і асинхронної лічильника лічильника; відрізняється подвійна система може бути розділена на двійкового лічильника і не-двійкового лічильника; процес підрахунку цифри щодо змін в тенденціях можна розділити на до лічильника, вниз лічильник і реверсивного лічильника.Введіть довічного лічильника Асинхронний двійковій Реверсивний лічильник На малюнку показаний 3-розрядного двійкового коду вниз лічильник асинхронний логічна схема і діаграма станів. Почніть з початкового стану 000, в перші лічильні імпульси після запуску FF0 фліп від 0 до (запозичувати сигналу Q0) 1, що робить це зростання FF1 також перевернув від 0 до 1 (Q1 запозичення сигналу), Передній фронт і зробити FF2 фліп від 0 до 1, тобто лічильник 000 в 111 державою. У цьому процесі, Q0 до Q1 є позика трохи, Q1 до Q2 для позички. З тих пір, кожен розраховує вхідних імпульсів, то лічильник зменшується в двійковому стані (мінус 1). Після введення перших восьми пунктів обвинувачення, лічильник назад в 000 держави, для завершення циклу. Таким чином, двійковий лічильник 23 (по модулю 8) Асинхронний реверсивний лічильник, який також має ефект частоти. Таким чином, асинхронний двійковий лічильник узагальнені в наступних пунктах: (1) н-трохи асинхронний двійковий лічильник нараховує п-го робочого стану (D тригера, так що Di = Цинь; JK-тригер, тому Джі = Ki = 1) з тригерів. Зв'язки між кожного тригера визначається додавання, методу підрахунку віднімання та тригера запуску. Для отримання додаткової лічильника і по фронту тригерів з, повинні термінал Q з тригера низьким тактовим входом сусідній тригера підключений до високої (тобто сигнал перенесення терміналу добротності тригера слід звернути); Якщо композиція з падінням по фронту тригера, тригер повинна бути низькою і ферзевом фланзі поруч з високим тактовий вхід тригера підключений. Для реверсивного лічильника, з'єднання протилежних кожного тригера. Може бути досягнуто після (2) в асинхронному довічного лічильника, держава повинна створити високу сальто тригер сигнал перенесення (рахунки) або сигнал (вниз підрахунку) запозичувати в низькому одного тригера. Цей тип лічильника також відомий як послідовний лічильник. Через це, тим нижче швидкість роботи асинхронний лічильник. Двійковій синхронного лічильника З метою підвищення швидкість рахунку, синхронні лічильники можуть бути використані, який характеризується підрахунку імпульсів одночасно підключених до тактовий вхід тригера вами, коли лічильний імпульс приходить, тригери спрацьовують одночасно, він повинен одночасно викликати фліп фліп немає затримки на всіх рівнях, що накопичилися. Синхронні лічильники можна також назвати паралельні лічильники. Двійковій синхронного лічильника Малюнок 8.4.5 з JK-тригера (але призвели до J = K), що складається з чотирьох довічних (М = 16) синхронізувати лічильник. Видно, тактовий вхід припинення тригера ви розраховувати той же імпульси CP, тригери наводяться рівняння J0 = К0 = 1, J1 = K1 = Q0, J2 = k2 = Q0Q1, J3 = K3 = Q0Q1Q2. Спосіб відповідно до тимчасової синхронізації ланцюга, стан схема таблиці отримані, як показано в таблиці 8.4.1. Нехай почати з початку 0000 станів, тому що J0 = К0 = 1, тому кожен лічильник імпульсів вхідного СР, низька тригер FF0 б перевернути один раз, інші біти викликає FFI тільки Джі = Гі = Ци-1Qi-2 ...... При виконанні умов Q0 = 1, і коли CP задньому фронту фліп. Малюнок 8.4.5 8.4.6 представляє собою тимчасову діаграму схеми, де пунктирна лінія є форма хвилі затримки передачі часу вважається тригерів після т на добу. На цьому малюнку показано, лічильник синхронізації, лічильник імпульсів СР кожному одночасно тригера, все шльопанці перевертаються одночасно, ніж лічильник імпульсів СР є часовий лаг ефект тонн в день, і, отже, швидкість роботи, ніж загальне асинхронний лічильник високою. Слід зазначити, що синхронізація лічильник асинхронний лічильник структура складна, ніж схема необхідно збільшити число вхід схеми управління, і таким чином обмежує швидкість роботи ланцюга управління також страждають від часу затримки передачі. Якщо тригер схема рис 8.4.5 FF1, FF2 і FF3, відповідно, сигнал збудження Двійковій синхронної реверсивний лічильник Практичні додатки, які іноді можуть вимагати лічильник для підрахунку може бути знижена рахунок. В обох плюс і мінус два яка вважає функція називається реверсивний лічильник лічильник. 4 двійковій синхронної реверсивний лічильник, як показано на малюнку 8.4.7, це в 4-розрядного двійкового синхронного лічильника плюс і мінус на основі описаного вище, додавши ланцюгів управління. Малюнок показує, що тригери наводяться рівняння Коли вгору / вниз керуючий сигнал, коли X = 1, FF1-FF3 кожного J, K і Q, відповідно, в кінці кожного нижнього кінця спусковий гачок включений, відлік зростає, а коли X = 0, коли J, K, відповідно, і кінець Питання термінал тригерів включений низький, відлік для досягнення функцію реверсивного лічильника Принцип Аналіз Структура ланцюга Крім трьох асинхронного двійкового лічильника, наприклад, як показано на малюнку 8.4.1. Схема складається з трьох по фронту D тригерів, з урахуванням таких особливостей: кожна з D тригера вхідний висновок тригера Q складу сигналу, таким чином Q н 1 = Q п, тобто, D тригерів знаходяться в підрахунку державної; вважаючи запускає імпульс у низькій терміналу С, Q висновок кожного тригера прийому сигналу з суміжних С-кінцевий високою. Принцип Аналіз Покладемо, що всі тригери в стан 0, у відповідності зі структурними характеристиками і тригер схеми експлуатаційних характеристик, то легко отримати свої діаграма станів і тимчасові діаграми, які показані на малюнку 8.4.2 і рис 8.4.3. Де пунктирна лінія вважається тригер сигналу затримки поширення Час т на добу після. Може бути добре видно з діаграми станів, починаючи з початкового стану 000 (як встановлено чіткого імпульсу), один рахунок для кожного вхідного імпульсу, стан лічильника збільшується на довічним (плюс 1), введіть перші вісім розраховує, лічильник і повернутися до 000 держав. Таким чином, це плюс 23 гекс лічильник, також відомий як матриця вісім (M = 8), а також лічильник. Може бути добре видно з тимчасової діаграми Q0, Q1, Q2, відповідно, число циклів в два рази пульс (СР) період у 4 рази, в 8 разів, тобто Q0, Q1, Q2, відповідно, двох сигналів СР частот, розділені на чотири, вісім частот, і, таким чином, лічильник може також бути використаний як роздільники. Слід зазначити, що, видно з сигналу пунктирною лінією на рис 8.4.3, при розгляді часу затримки передачі т на добу тригерів, для п-біт асинхронного двійкового лічильника, лічильник від імпульсу (наростаючий фронт функція безлічі ) підходить до фліп н перекрутився стабільні, ви повинні випробувати найдовший час п'рд, щоб забезпечити статус лічильника може підрахувати кількість імпульсів правильної реакції, на наступний рахунок імпульсів (зростання) повинні прийти після NTPD, і, отже, Мінімальна кількість цикл імпульсів Tmin = NTPD. |

| Користувач Огляд |

|

Немає коментарів |